# Onsemi

# **Inductive Position Sensor** with Battery Backup

# Resolution: Single-Turn 20-bit / Multi-Turn 24-bit

# NCS32100

The NCS32100 is a full featured controller and sensor interface for high resolution, high accuracy angular sensing solutions when paired with a contactless PCB sensor. This device supports static to high-speed applications. The NCS32100 has flexible configuration capabilities allowing for connection to a variety of inductive sensor patterns and offers absolute serial digital output. Inductive sensing techniques have unique advantages over traditional position sensor solutions including but not limited to contaminant insensitivity, mechanical simplification, as well as providing an overall lower cost sensor solution.

# Features

- Provides Absolute Position Output with Programmable Index

- Provides Velocity, Temperature, and Backup Battery Measurements

- Supports Connection to an RS-485 Driver (2.5 Mbps)

- Maximum Speed at Full Accuracy: 6000 rpm

- Maximum Speed at Reduced Accuracy: 60,000 rpm

- Supply Voltage Range: 2.75 V 5.5 V

- Interface level shifting from 2.7 V to 5.5 V

- Low Power Battery Mode Consumption: 2 mA (Typical)\*

- Full Operation Current Consumption 80 mA (Typical)

- Internal Programmable M0-ARM MCU Provides Data Interface, Configuration, NVM, and Calibration Features

- This Device is Pb-Free and is RoHS Compliant

# **Typical Applications**

- Industrial Automation / Robotics

- Motor Control / Positioning

- Servo Applications

\*Battery mode consumption is based on wakeup duty cycle timing defined by firmware

# SENSOR DEPENDENT METRICS (Note 1)

| Accuracy             | PCB Sensor              |

|----------------------|-------------------------|

| ±50 arcsec or better | OD: 37.5 mm<br>ID: 8 mm |

1. Overall accuracy can be increased by using larger diameter sensors; the NCS32100 supports up to 18 bits of accuracy.

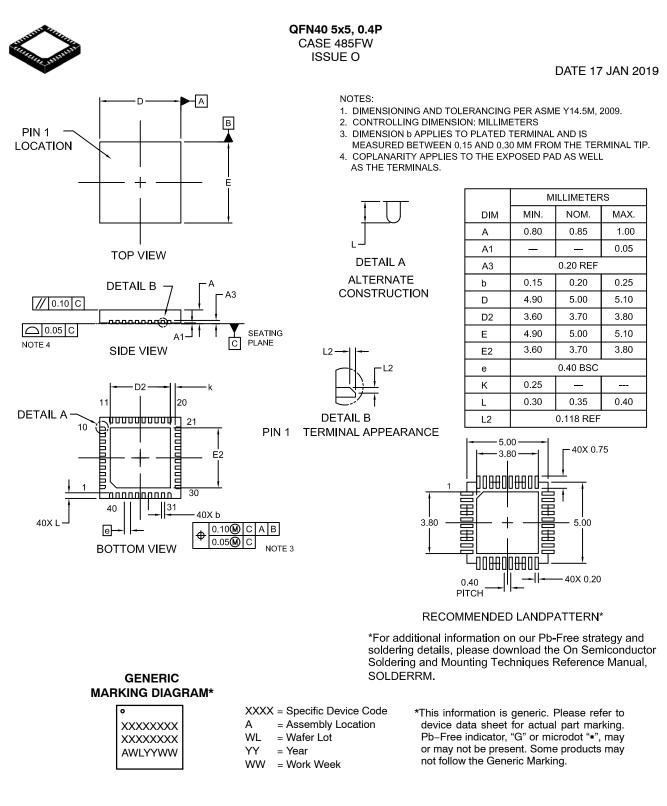

#### MARKING DIAGRAM

А

1

YY

WW

# = Work Week

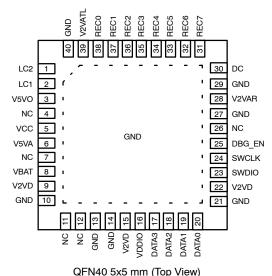

# **PIN CONFIGURATION**

# **ORDERING INFORMATION**

| Device         | Package   | Shipping <sup>†</sup> |  |  |  |  |  |

|----------------|-----------|-----------------------|--|--|--|--|--|

| NCS32100XMNTXG | QFN40     | 5000 / Tape<br>& Reel |  |  |  |  |  |

| NCS32104XMNTBG | (Pb-Free) | 1500 / Tape<br>& Reel |  |  |  |  |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

NOTE: Internal power distribution lines from Power Supply block and bypass pin are not shown.

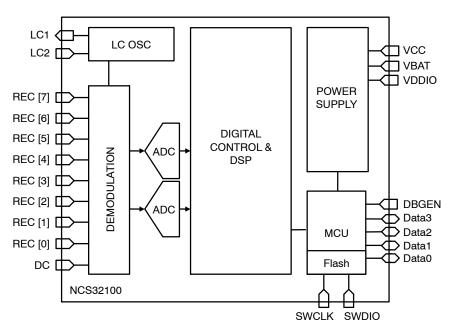

Figure 1. Block Diagram

# **Operating Description**

The block diagram shown in figure 1 describes the basic contents of the NCS32100. The NCS32100 is a multichip module contained in a single 5 mm x 5 mm package. The NCS32100 contains an internal oscillator for driving the primary sensor excitation coil, as well as demodulation circuitry for receiving the inductively coupled sensor signals on the REC[n] pins. The applications section of this data sheet further defines connection to these pins. Two 12–bit ADCs digitize the demodulated signals. These digitized values are then passed to the DSP block for processing. Position and speed information are then passed from the

digital block to the internal MCU. Digital position and velocity data is then sent out on the Data[3:0] pins made available for external drive circuitry, such as an RS-485 driver. The protocol and timing of the commands and data on the data pins are defined by the internal MCU firmware. The MCU also handles calibration routines for maximizing accuracy when the NCS32100 is paired with a sensor. The NCS32100 houses power supply circuitry supporting a wide VCC range and battery backup capability. The internal MCU's non-volatile memory is included for the storage of calibration parameters and sensor front end configuration.

# Table 1. NCS32100 PIN DESCRIPTION

| Pin                                  | Pin Name | Digital /<br>Analog: I/O | Recommended Connection                                                                                                                                                           | Description                                                                                                                                                          |

|--------------------------------------|----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2                                 | LC2, LC1 | Analog I/O               | Connect to excitation coil and<br>matching capacitors                                                                                                                            | Oscillator coil drive outputs                                                                                                                                        |

| 3                                    | V5VO     | Supply Output            | Connect to V5VA                                                                                                                                                                  | LC Oscillator Power                                                                                                                                                  |

| 4, 7, 11,<br>12, 13, 26              | NC       | NC                       | Connect to ground                                                                                                                                                                | NC                                                                                                                                                                   |

| 5                                    | VCC      | Supply Input             | Connect to 5 V Supply and bypass capacitor (10 $\mu$ F)                                                                                                                          | Primary 5 V Supply                                                                                                                                                   |

| 6                                    | V5VA     | Supply Output            | Connect to bypass capacitor<br>(10 μF)                                                                                                                                           | 3 V/5 V Supply for internal LC oscillator (Connect to external local bypass capacitor).                                                                              |

| 8                                    | VBAT     | Supply Input             | Connect to 3 V backup battery and bypass capacitor (100 $\mu\text{F})$                                                                                                           | Optional: Backup 3 V battery supply pin (Connect to external battery if using battery backup). Connect to ground through 100 k $\Omega$ if not using battery backup. |

| 9, 22, 15                            | V2VD     | Supply Output            | Connect to bypass capacitor<br>(1 µF)                                                                                                                                            | Digital supply observation pin (Connected to local bypass capacitance for better noise performance)                                                                  |

| 10, 14, 21,<br>27, 29, 40,<br>41     | GND      | Ground Returns           | Connect to ground                                                                                                                                                                | 0 V Return, connect to module ground                                                                                                                                 |

| 16                                   | VDDIO    | Supply Input             | 3 V to 5 V. Connect to External<br>Driver Supply (RS-485 driver)                                                                                                                 | I/O power supply for Data[3:0] pins                                                                                                                                  |

| 17                                   | Data3    | Digital I/O              | Connect to data input or output<br>depending on configuration                                                                                                                    | $\text{RX} \rightarrow \text{Data}$ from External Master to NCS32100                                                                                                 |

| 18                                   | Data2    | Digital I/O              | Connect to data input or output<br>depending on configuration                                                                                                                    | $TX \to Data$ from NCS32100 to External Master                                                                                                                       |

| 19                                   | Data1    | Digital I/O              | Connect to data input or output depending on configuration                                                                                                                       | Available GPIO                                                                                                                                                       |

| 20                                   | Data0    | Digital I/O              | Connect to data input or output depending on configuration                                                                                                                       | TX_EN $\rightarrow$ Enable signal for RS485 External Transceiver                                                                                                     |

| 23                                   | SWDIO    | Digital Input            | Connect to ground when not<br>programming internal MCU                                                                                                                           | Serial Wire Data (MCU firmware data pin)                                                                                                                             |

| 24                                   | SWCLK    | Digital Input            | Connect to ground when not<br>programming internal MCU                                                                                                                           | Serial Wire Clock (MCU firmware clock pin)                                                                                                                           |

| 25                                   | DBG_EN   | Digital Input            | Connect to ground when not<br>programming internal MCU                                                                                                                           | MCU debug Enable pin (Assert high to program / debug internal MCU)                                                                                                   |

| 28                                   | V2VAR    | Supply Output            | Connect to V2VATL (1 $\mu$ F)                                                                                                                                                    | Analog Power (internally regulated)                                                                                                                                  |

| 30                                   | DC       | Analog Input             | Connect to DC coil (coupled to excitation coil) If using a capacitive divider in place of the DC coupling coil, then connect DC to ground through a $0.1 \mu\text{F}$ capacitor. | Receiver Coil DC Bias                                                                                                                                                |

| 31, 32, 33,<br>34, 35, 36,<br>37, 38 | REC[7:0] | Analog I/O               | Connect to Fine and Coarse<br>Receiver Coils, Configuration<br>for Coarse versus Fine can be<br>set via internal registers                                                       | Receiver Coils [7:0]                                                                                                                                                 |

| 39                                   | V2VATL   | Supply Input             | Connect to bypass capacitor<br>(0.1 μF)                                                                                                                                          | Supplied by connection to V2VAR externally                                                                                                                           |

#### Table 2. ABSOLUTE MAXIMUM RATINGS

| Rating                                                         | Symbol                | Value      | Unit |

|----------------------------------------------------------------|-----------------------|------------|------|

| Supply Voltage Range                                           | V <sub>CC</sub>       | –0.3 to 6  | V    |

| VBAT Voltage Range                                             | V <sub>BAT</sub>      | –0.3 to 6  |      |

| Thermal Resistance, Junction-to-Ambient, Steady State (Note 2) | $R_{	heta JA}$        | 32         | °C/W |

| Thermal Resistance, Junction-to-Case (VIN Paddle)              | $R_{	extsf{	heta}JC}$ | 0.98       | °C/W |

| Storage Temperature Range                                      | T <sub>STG</sub>      | -40 to 150 | °C   |

| Lead Temperature, Soldering (10 Sec.)                          | T <sub>SLD</sub>      | 260        | °C   |

| ESD Capability, Human Body Mode (Note 3)                       | ESD <sub>HBM</sub>    | 2          | kV   |

| ESD Capability, Charged Device Mode (Note 3)                   | ESD <sub>CDM</sub>    | 0.5        | kV   |

| Latch-up Current Immunity (Note 3)                             | LU                    | 100        | mA   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2. Surface-mounted on FR4 board using the minimum recommended pad size, 1 oz Cu.

Tested by the following methods @ T<sub>A</sub> = 25°C: ESD Human Body Model tested per JS-001-2017

ESD Human Body Model tested per JS-001-2017 ESD Charged Device Model per JS-002-2018 Latch-up Current tested per JESD78

#### **Table 3. OPERATING CONDITIONS**

| Rating                                          | Symbol           | Min   | Тур | Max   | Unit |

|-------------------------------------------------|------------------|-------|-----|-------|------|

| Excitation Frequency Range                      | F <sub>OSC</sub> | 3     | 4   | 6     | MHz  |

| VCC                                             | V <sub>CC</sub>  | 2.75  | 5.0 | 5.5   | V    |

| V <sub>BAT</sub>                                | V <sub>IN</sub>  | 2.75  | 3.3 | 4.2   | V    |

| VCC – V <sub>BAT</sub> (Note 4)                 | V <sub>NOM</sub> | 0.3   | 0.7 | 5.5   | V    |

| GND Pins                                        | V <sub>SS</sub>  | -     | 0   | -     | V    |

| REC Pins Input Voltage Amplitude (Peak to Peak) | V <sub>REC</sub> | 0.015 | -   | 0.120 | Vpp  |

| Ambient Temperature (Note 5)                    | T <sub>A</sub>   | -40   | -   | 85    | °C   |

| Junction Temperature                            | ТJ               | -40   | -   | 105   | °C   |

| Multi-turn Count Range                          | MT               | -     | -   | 24    | bits |

| Position Resolution                             | ST               | -     | -   | 20    | bits |

| Velocity Resolution                             | Vel              | -     | -   | 20    | bits |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

VCC-V<sub>BAT</sub> is the voltage difference between VCC and V<sub>BAT</sub> required to stay in normal mode. Dropping below this voltage will enter the part into battery mode.

5. Minimum ambient temperature is qualified to -40°C. The maximum ambient temperature is dependent on the self-heating of the device, which is dominated by the excitation coil drive. Larger airgaps between rotor and stator induce larger excitation coil current drive and higher self-heating. The NCS32100 is qualified up to 85°C ambient operational temperature.

# Table 4. ELECTRICAL CHARACTERISTICS (T<sub>J</sub> = $25^{\circ}$ C, V<sub>CC</sub> = 3 V – 5.5 V, unless otherwise specified)

| Parameter                            | Condition                                               | Symbol            | Min | Тур | Max | Unit |

|--------------------------------------|---------------------------------------------------------|-------------------|-----|-----|-----|------|

| Supply Battery Mode Current (Note 6) | $V_{CC} = 0 \text{ V}, \text{ V}_{BAT} = 3.3 \text{ V}$ | I <sub>STBY</sub> | 0.2 | 2   | 5   | mA   |

| VBAT DC reverse current (Note 7)     | $V_{CC}$ = 5 V, $V_{BAT}$ = 3.3 V, T = 85°C             | I <sub>VBAT</sub> | -   | 1   | -   | μΑ   |

| Supply Dynamic Current               | V <sub>CC</sub> = 5.0 V                                 | I <sub>DYN</sub>  | 82  | 90  | 133 | mA   |

| Data[3:0] Pin Drive Strength         | V <sub>CC</sub> = 5.0 V                                 |                   | -   | 2   | -   | mA   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

6. Max battery current draw during battery mode assumes a 10 ms wakeup cycle. Min battery current draw during battery mode assumes no periodic wakeup cycles. The wakeup period controls how often the NCS32100 takes a measurement from the sensor coils to track turns count. Battery current during battery mode can be reduced by slowing down the wakeup period, but that will also reduce the rotor speed at which turn counts can be tracked. See the NCS32100 Reference Design Manual for more information on battery mode.

7. Typical reverse current on VBAT is on the order of nano amps. Under certain conditions transient reverse current may occur on VBAT, but will not exceed 100 nano coulumbs.

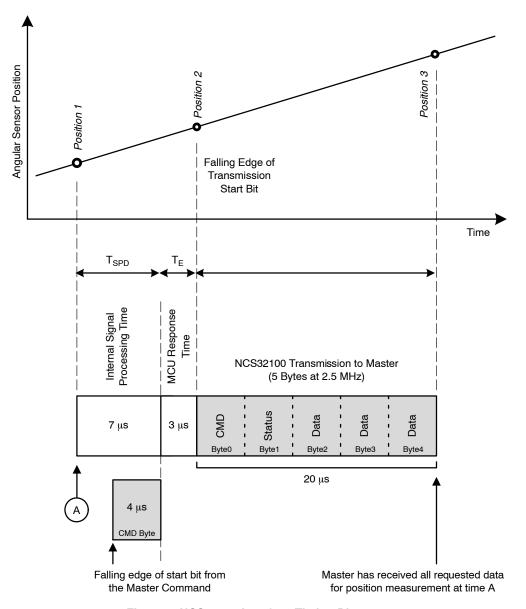

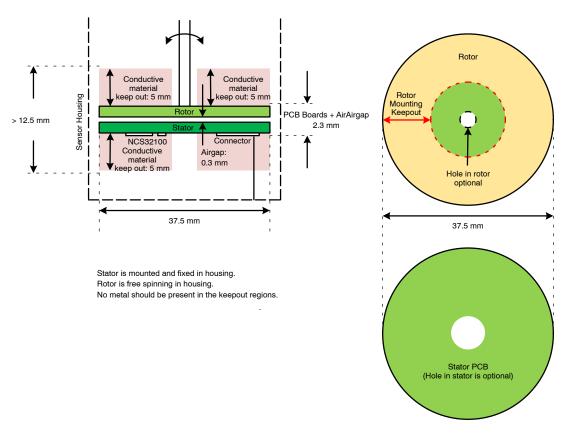

#### NCS32100 TIMING SPECIFICATIONS

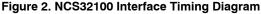

The NCS32100 defaults to output 'Position 1', as described in figure 2. The actual position of the sensor shaft at the time the position is reported to the external RS485 driver will be different than what is reported if the shaft speed is not zero due to latency in the system. The time elapsed from initial angle sample on the REC pins of the NCS32100 to the falling edge of the start bit in the RS485 transmission of the digitized position data can be quantified as the signal processing delay plus the time it takes the MCU to acquire the digitized data and format it to the output protocol ( $T_{SPD} + T_E$ ). The MCU acts as the internal master, and its communications with the signal processing block are synchronous with the timing of the signal processing. T<sub>E</sub> defines the time required for communication between the signal processing and the MCU. The DSP offers a delay compensation feature, where the signal processing delay is

compensated for and 'Position 2' position is reported. 'Position 2' is an extrapolation based on previous positions and the current velocity of the sensor. 'Position3' could be reported as the output if desired by configuring the extrapolation filter out even further. 'Position 1' will be reported by default, where the extrapolation is bypassed. Delay compensation can be configured with the proper internal register setting (detailed in the NCS32100 configuration section). Timing determination should always be referenced from the falling edge of the NCS32100 response start bit and not the master command, as the masters command is asynchronous with the internal signal processing, and the duration of the command is user defined through the MCU firmware. If the rotor is stationary, then position 1, position 2, and position 3 would all be the same value.

# Table 5. NCS32100 TIMING SPECIFICATIONS (T<sub>J</sub> = $25^{\circ}$ C, V<sub>CC</sub> = 3 V – 5.5 V, unless otherwise specified)

| Parameter                                                          | Condition                        | Symbol           | Min    | Тур  | Max   | Unit    |  |

|--------------------------------------------------------------------|----------------------------------|------------------|--------|------|-------|---------|--|

| Position Sample Throughput (Available to<br>Internal MCU) (Note 8) | V <sub>CC</sub> = 5.0 V          | T <sub>TP</sub>  | 500 ns | 1    | 2     | μs      |  |

| Position Sample Latency (Un-compensated)                           | V <sub>CC</sub> = 5.0 V          | T <sub>SPD</sub> | -      | 7    | -     | μs      |  |

| MCU Latency (Note 9)                                               | V <sub>CC</sub> = 5.0 V          | Τ <sub>Ε</sub>   | -      | 3    | -     | μs      |  |

| Max Velocity (Note 10)                                             | V <sub>CC</sub> = 5.0 V          | V <sub>MAX</sub> | -      | 6000 | 45000 | Rev/min |  |

| Max MCU to SFE Timing Jitter (Note 8)                              |                                  | Tjitter          | 0      | 0.25 | 0.5   | μs      |  |

| UART Transmission Rate                                             |                                  |                  | -      | -    | 2.5   | MHz     |  |

| Power Up Ready Time                                                |                                  |                  | -      | -    | 50    | ms      |  |

| Self Calibration Run Time (Note 11)                                |                                  |                  | -      | 2    | -     | S       |  |

| External Calibration Run Time                                      | 1 full revolution at 100 rpm max |                  | 2      | -    | -     | s       |  |

8. Updated position data is available for acquisition by the internal MCU every T<sub>TP</sub> 500 ns can be achieved by enabling internal oversampling

8. Opdated position data is available for acquisition by the internal MCU every 1<sub>TP</sub>, 500 hs can be achieved by enabling internal oversampling filter. If the digital filter is bypassed, then the updated position is available to the MCU every 2 μs.

9. T<sub>E</sub> assumes direct MCU pass through. Any additional processing in the MCU will add latency.

10. Accuracy may exceed 50 arcsec beyond 6000 rpm due to the system sampling jitter of 500 ns. 45,000 RPM max rotor speed assumes fine sensor on stator has 64 periods. Faster speeds can be achieved with lower supported period options. See application section for details.

11. The calibration routine can be run on an external processor at much higher speeds (~2 seconds with high performance MCU), or it can be run other internal when internal MCU firmware).

run directly by the NCS32100 (as implemented in the internal MCU firmware).

# NCS32100 EXTERNAL COMPONENT SPECIFICATIONS

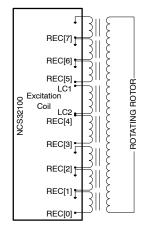

The NCS32100 requires a minimal number of external components to function as a system. This is comprised of bypass capacitors for the supply pins, tuning capacitors for the LC Oscillator pins, and the external sensor coils connected to the LC Oscillator pins and the Receiver pins. The excitation coil (connected from the LC1 pin to the LC2 pin) is used to provide the excitation field, which creates eddy currents in the rotor coils. The eddy currents in the rotor inductively couple to the receiver coils to induce voltages that are proportional to the position of the rotor (which is in

close proximity)., The receiver signals are connected to pins REC[7:0]. The orientation of the receiver coils and the excitation coil is discussed in more detail in the applications section. The diagram below shows the external components with their value definition found in Table 6. The excitation frequency is determined by the equation  $F_{EXT} = 2\pi \sqrt{L_{OSC}C_{EQ}}$ . Where  $C_{EQ}$  is the equivalent capacitance of the two external capacitors as if they are connected in series. The excitation coil should be designed with the right value of capacitors to target 4.4 MHz for the excitation frequency.

Figure 3. External Component Placement Diagram

| Parameter                            | Condition                        | Symbol                  | Min  | Тур | Max  | Unit |

|--------------------------------------|----------------------------------|-------------------------|------|-----|------|------|

| Receiver Coil Series Resistance      |                                  | ESR <sub>COIL</sub>     | -    | 4   | -    | Ω    |

| LC Oscillator Coil Inductance        |                                  | LLC_OCS_COIL            | 0.5  | 1   | 4    | μH   |

| LC Oscillator Coil Series Resistance |                                  | $ESR_{LC}_{OSC}_{COIL}$ | -    | 0.5 | 1.0  | Ω    |

| LC Oscillator Load Capacitance       |                                  | C <sub>LC</sub>         | 0.35 | 3.2 | 11.3 | nF   |

| Power Supply Decoupling Capacitors   | Used for V2VATL, V2VAR, and V2VD | C <sub>2</sub>          | 0.8  | 1.0 | 1.2  | μF   |

| Power Supply Decoupling Capacitors   | Used for VCC, V5VA, and V5VO     | C <sub>1</sub>          | 8    | 10  | 12   | μF   |

| VBAT Decoupling Capacitors           | VBAT supply decoupling capacitor | C <sub>BAT</sub>        | 100  | _   | 260  | μF   |

NOTE: Refer to reference design manual for sensor design details. Table 6 is intended as preliminary guidance only.

# CONFIGURATION

The analog front end internal to the NCS32100 communicates with the embedded MCU via a 16-bit 40 MHz parallel bus. The NCS32100 firmware includes subroutine functions that enable communication with the front end on this parallel bus. Data can be acquired such as position, and velocity. The firmware allows access to the internal configuration registers that control the functionality of the part. These configuration registers are loaded from the MCU non-volatile memory as part of the start-up routine. Configuration can be changed after initial startup. The reference firmware allows for reading and writing these configuration registers, and any changes will be saved to the MCU non-volatile memory. Once the part is configured and data is received across the internal parallel bus, the embedded MCU can format the data and transmit it to an external master per request according to the protocol definition implemented in the firmware. Please refer to the NCS32100 reference design manual for a detailed description of the firmware functionality and the interface implementation. The NCS32100 is loaded with the reference design firmware by default, which properly handles the configuration during start–up.

# NCS32100 Configuration Table

The table below details the configuration registers accessed by the embedded MCU. The purpose of each register is defined in Appendix A. These registers are all properly handled in the reference design firmware. Modification can be made by the user as needed. The NCS32100 is highly configurable. Application notes are provided upon request detailing advanced configuration options.

| Address                                    | Access Type                                            | Description                                                                                  | Default Value         |

|--------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------|

| 0x00                                       | R                                                      | LC Oscillator Gain DAC (Status only)                                                         | 0x0000 (Note 12)      |

| 0x01                                       | R                                                      | PGA Gain DAC (Status only)                                                                   | 0x0000 (Note 12)      |

| 0x03                                       | R                                                      | Digital Control (Status only)                                                                | 0x0000                |

| 0x04                                       | R                                                      | Status                                                                                       | 0x0000 (Note 12)      |

| 0x10                                       | R/W                                                    | Selection Matrix for Coarse Block                                                            | 0xF249                |

| 0x11                                       | R/W                                                    | Selection Matrix for Fine Block                                                              | 0x0B6D                |

| he next 16 register<br>le analog front–end | s (0x12 through 0x21) ho<br>d. See the calibration sec | Id the calibration coefficients used to calibrate out any asymmetries tion for more details. | in the PCB sensor and |

| 0x12                                       | R/W                                                    | Clarke Transform Imaginary Coefficient 0 for Coarse Block                                    | 0x0000 (Note 12)      |

| 0x13                                       | R/W                                                    | Clarke Transform Imaginary Coefficient 1 for Coarse Block                                    | 0x0000 (Note 12)      |

| 0x14                                       | R/W                                                    | Clarke Transform Imaginary Coefficient 2 for Coarse Block                                    | 0x0000 (Note 12)      |

| 0x15                                       | R/W                                                    | Clarke Transform Imaginary Coefficient 3 for Coarse Block                                    | 0x0000 (Note 12)      |

| 0x16                                       | R/W                                                    | Clarke Transform Real Coefficient 0 for Coarse Block                                         | 0x0000 (Note 12)      |

| 0x17                                       | R/W                                                    | Clarke Transform Real Coefficient 1 for Coarse Block                                         | 0x0000 (Note 12       |

| 0x18                                       | R/W                                                    | Clarke Transform Real Coefficient 2 for Coarse Block                                         | 0x0000 (Note 12)      |

| 0x19                                       | R/W                                                    | Clarke Transform Real Coefficient 3 for Coarse Block                                         | 0x0000 (Note 12)      |

| 0x1A                                       | R/W                                                    | Clarke Transform Imaginary Coefficient 0 for Fine Block                                      | 0x0000 (Note 12)      |

| 0x1B                                       | R/W                                                    | Clarke Transform Imaginary Coefficient 1 for Fine Block                                      | 0x0000 (Note 12)      |

| 0x1C                                       | R/W                                                    | Clarke Transform Imaginary Coefficient 2 for Fine Block                                      | 0x0000 (Note 12)      |

| 0x1D                                       | R/W                                                    | Clarke Transform Imaginary Coefficient 3 for Fine Block                                      | 0x0000 (Note 12)      |

| 0x1E                                       | R/W                                                    | Clarke Transform Real Coefficient 0 for Fine Block                                           | 0x0000 (Note 12)      |

| 0x1F                                       | R/W                                                    | Clarke Transform Real Coefficient 1 for Fine Block                                           | 0x0000 (Note 12)      |

| 0x20                                       | R/W                                                    | Clarke Transform Real Coefficient 2 for Fine Block                                           | 0x0000 (Note 12)      |

| 0x21                                       | R/W                                                    | Clarke Transform Real Coefficient 3 for Fine Block                                           | 0x0000 (Note 12)      |

| 0x22                                       | R/W                                                    | Velocity Coefficient MSB for Absolute Algorithm Extrapolation                                | 0x0000                |

| 0x23                                       | R/W                                                    | Velocity Coefficient LSB for Absolute Algorithm Extrapolation                                | 0x7E75                |

| 0x26                                       | R/W                                                    | Velocity Coefficient MSB for Digital Filter Extrapolation                                    | 0x0084                |

| 0x27                                       | R/W                                                    | Velocity Coefficient LSB for Digital Filter Extrapolation                                    | 0x0561                |

# Table 7. NCS32100 SHADOW REGISTERS TO BE LOADED BY THE EMBEDDED MCU

| Table 7. NCS32100 SHADOW REGISTERS TO BE LOADED BY THE EMBEDDED MCU (continu | ued) |

|------------------------------------------------------------------------------|------|

|------------------------------------------------------------------------------|------|

| Address | Access Type | Description                        | Default Value |

|---------|-------------|------------------------------------|---------------|

| 0x2A    | R/W         | Low Pass Filter for Digital Filter | 0x003F        |

| 0x2B    | R/W         | Digital Control                    | 0x0020        |

| 0x2F    | R/W         | Channel Select                     | 0x0000        |

| 0x40    | R/W         | LC Oscillator Gain DAC Control     | 0x0000        |

| 0x41    | R/W         | LC Oscillator Gain Time Control    | 0x01F4        |

| 0x42    | R/W         | PGA Coarse Gain DAC Control        | 0x0000        |

| 0x43    | R/W         | PGA Fine Gain DAC Control          | 0x0000        |

| 0x44    | R/W         | PGA Gain Time Control              | 0x01F4        |

| 0x45    | R/W         | PGA Coarse Offset DAC Control      | 0x0000        |

| 0x46    | R/W         | PGA Fine Offset DAC Control        | 0x0000        |

| 0x47    | R/W         | PGA Offset Time Control            | 0x01F4        |

| 0x48    | R/W         | Angle Extrapolator Time Control    | 0x0000        |

| 0x4C    | R/W         | Normal Wakeup Delay                | 0x1000        |

| 0x4D    | R/W         | Startup Delay Time MSB             | 0x0006        |

| 0x4E    | R/W         | Startup Delay Time LSB             | 0x1A80        |

| 0x4F    | R/W         | DSP Wakeup Delay                   | 0x1000        |

| 0x50    | R/W         | Autozero Angle MSB                 | 0x0000        |

| 0x51    | R/W         | Autozero Angle LSB                 | 0x0000        |

| 0x57    | R/W         | Input/Output Control               | 0x0008        |

| 0x5F    | R/W         | Sensor Selection                   | 0x0013        |

| 0x80    | R/W         | Secondary Calibration Bin 0        | 0x0000        |

| 0x81    | R/W         | Secondary Calibration Bin 1        | 0x0000        |

| 0x82    | R/W         | Secondary Calibration Bin 2        | 0x0000        |

| 0x83    | R/W         | Secondary Calibration Bin 3        | 0x0000        |

| 0x84    | R/W         | Secondary Calibration Bin 4        | 0x0000        |

| 0x85    | R/W         | Secondary Calibration Bin 5        | 0x0000        |

| 0x86    | R/W         | Secondary Calibration Bin 6        | 0x0000        |

| 0x87    | R/W         | Secondary Calibration Bin 7        | 0x0000        |

| 0x88    | R/W         | Secondary Calibration Bin 8        | 0x0000        |

| 0x89    | R/W         | Secondary Calibration Bin 9        | 0x0000        |

| 0x8A    | R/W         | Secondary Calibration Bin 10       | 0x0000        |

| 0x8B    | R/W         | Secondary Calibration Bin 11       | 0x0000        |

| 0x8C    | R/W         | Secondary Calibration Bin 12       | 0x0000        |

| 0x8D    | R/W         | Secondary Calibration Bin 13       | 0x0000        |

| 0x8E    | R/W         | Secondary Calibration Bin 14       | 0x0000        |

| 0x8F    | R/W         | Secondary Calibration Bin 15       | 0x0000        |

| 0x90    | R/W         | Battery Mode Wakeup Period Setting | 0X0100        |

12. NCS32100 will determine values based on sensor characteristics.

# Internal Data Format (As Received across the 16-bit Interface)

The position, velocity, and turns count as received from the data acquisition functions are shown in the table below.

| Data     | Bits | Sign     | Scale           | Description                                                                                                                                                               |  |

|----------|------|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Angle    | 20   | Unsigned | 2 <sup>20</sup> | Angle is an unsigned 20 bits measurement of the absolute angle in 1 revolution. In other words, the angle is represented as 1 to 1,048,576 in one revolution.             |  |

| Turn     | 24   | Signed   | 1               | Turn is a signed 24 bits measurement of the complete revolutions. Turn is increment by $+1$ for every clockwise rotation and by $-1$ for every counterclockwise rotation. |  |

| Velocity | 20   | Signed   | 2 <sup>29</sup> | Velocity is a signed 2's complement 20 bits measurement of the angular velocity per $\mu s$ .                                                                             |  |

# Table 8. NCS32100 DATA FORMAT DESCRIPTION

Below are examples that show how these formats can be converted to radians and degrees.

# **Angle Conversion**

Example: Received Angle hex value of 0x62626 (Decimal value is 402,982)

# Table 9. POSITION CONVERSION EXAMPLE

| To Convert to Radians                                                                    |                                         |  |  |

|------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| Received Position from NCS32100: 402,982                                                 |                                         |  |  |

| 1. Divide received value by scale (2^20).         402,982/1,048,576 = 0.384314 rotations |                                         |  |  |

| 2. Multiply by $2\pi$ to get radians                                                     | 0.384314 * 2π <i>= 2.41471 radians</i>  |  |  |

| Convert to Degrees                                                                       |                                         |  |  |

| 1. Divide received value by scale (2^20).         402,982/1,048,576 = 0.384314 rotations |                                         |  |  |

| 2. Multiply by 360 to get degrees                                                        | 0.384314 * 360 = <i>138.353 Degrees</i> |  |  |

# **Velocity Conversion**

Example: Received velocity is hex 0xBAADF (signed decimal -289,937)

# Table 10. VELOCITY CONVERSION EXAMPLE

| To Convert to Radians                                                                                      |                                              |  |  |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|

| Velocity received from the NCS32100: -289,937                                                              |                                              |  |  |

| 1. Divide received value by scale (2^29)         -289,937 / 536,870,912 = -0.00054 rotations/µs            |                                              |  |  |

| 2. Multiply by $2\pi$ to get radians                                                                       | –0.00054 * 2π = <i>–0.003393 radians/</i> μs |  |  |

| Convert to Degrees                                                                                         |                                              |  |  |

| 1. Divide received value by scale (2 <sup>2</sup> )         -289,937 / 536,870,912 = -0.00054 rotations/μs |                                              |  |  |

| 2. Multiply by 360 to get degrees                                                                          | -0.00054 * 360 = -0.1944 Degrees/µs          |  |  |

# **OTHER NCS32100 FEATURES**

# **Open Coil Detect**

The NCS32100 device has an open coil detect feature that can be used to detect if any sensor coils are not connected to the RECx pins (open circuit). If there is a break in one of the sensor coils, or if it is not connected, then running this test will result in a 0b'1 in the status register (register 0x04 bit 13). The Open Coil Detect test is run by writing the USER OPENCOILDET RUN bit to a 1 in Digital Control register (0x03 bit 13). This will start an Open Coil Detect test immediately. The USER\_OPENCOILDET\_RUN bit will high until the test has stav finished. The OPENCOILDET\_AT\_POR\_DIS bit in Digital Control register controls whether the Open Coil Detect test is run during startup. A value of 0b'1 in the bit will cause the test to not be run during startup. A value of 0b'0 will cause the test to be run at startup.

# **Extrapolation Tuning**

The NCS32100 device provides an extrapolation feature that can be used to cancel the effect of data reporting latency. When a request for the position is made, the data response comes with some latency. If the sensor is moving, then the position at the time the data is received will be different than it was at the time the request was made. Extrapolation can be used to predict where the sensor will be post latency so that the data readout will be the position at the time the data is received. The extrapolated angle relies on the current position and the current velocity. The extrapolation uses low pass filters on the velocity to make the future position prediction. The extrapolation calculation takes the form of:

$$\theta_{\text{EXT}} = \theta_{\text{LPF}} + K_{\text{v}} v_{\text{LPF}} + K_{\text{a}} a_{\text{LPF}}$$

(eq. 1)

Where is the angular velocity coefficient. is a programmable coefficient. The optimal value needs to be calibrated by the user.

The objective of setting the Kv constant is to effectively time shift angular measurements forward in time. From the perspective of the system, this time shift can cancel system delay to effectively create a zero delay system. From the perspective of the encoder, this is done by extrapolating the angular position forward in time using measured speed. However, no two systems are identical. Therefore, the Kv constant need to be determined for the given system using lab measurements.  $K_A$  is the angular acceleration coefficient. It is also programmable and should be set in the same fashion as the  $K_V$  coefficient. Please refer to the NCS32100 advanced configuration application note for details on calibrating these coefficients. The extrapolation feature can be disabled by setting the USER\_ABSALGO\_EXTRP\_DIS bit in the Digital Control register (0x03 bit 15). The extrapolation is bypassed by default in the NCS32100 firmware, and needs to be configured by the user if the extrapolation feature is needed.

# Sensor Calibration

Each PCB sensor design will include some systematic asymmetries that need to be calibrated for in both Fine and Coarse sensors. Calibration needs to take place to compensate for PCB mismatch, rotor air gap, tilt and eccentricity. The NCS32100 default firmware contains a self-calibration routine that allows for calibration independent of a reference. Calibration can be initiated from a master by command. The NCS32100 can also deliver raw samples that allow for external calibration with a reference encoder. For more information on the sensor calibration method, please refer to the NCS32100 Reference Design Manual.

For external calibration options, please request further documentation. Testing shows that re–calibration is not necessary to maintain 50 arcsec accuracy or less if the eccentricity and air gap do not vary by more than  $\pm 250 \,\mu\text{m}$  from center. The rotor must be centered to within 50  $\mu\text{m}$  to the shaft to allow for proper calibration. The reference design firmware includes the calibration routine and a method for secondary calibration allowing for the cancellation of 360 degree rotation single period fundamental or low spatial frequency error.

# **Battery Backup**

The NCS32100 supports a battery backup mode where VBAT can be tied to a 3.3V nominal external battery. The current draw from the battery during normal operation is <1 µA. When the VCC voltage drops below the VBAT voltage, the NCS32100 will switch over to draw current from the battery. During this time, the firmware running on the internal MCU puts the sensor front end to sleep to conserve power. The firmware periodically wakes up the sensor front end to take a position reading and to update the multi-turn count. The amount of current that is drawn from the battery depends on the wakeup period. The NCS32100 will be able to track turns count at higher speeds with shorter wakeup periods, but it will also consume more amortized current from the battery in battery mode. The NCS32100 Reference Design firmware allows the user to select the wakeup period to control the current draw and the turns count proficiency.

# APPLICATIONS INFORMATION

# **MCU** Capabilities

The internal MCU allows for the addition of several features defined by the MCU firmware. The embedded MCU firmware is ultimately responsible for defining the output protocol and timing. Once the data is available in the MCU, it can be manipulated by the firmware for output. Possibilities for additional features include (but are not limited to):

# Flexible Protocols

The internal MCU firmware can be written to change the protocols used for communication in absolute encoder mode.

# Error Reporting

Error reporting can be implemented by writing the MCU firmware to recognize and handle specific errors. The MCU has access to registers in the digital control block, including the calibration coefficients and the gain settings for the coil drivers. The MCU can be programmed to monitor gain settings to detect if the sensor signal strength is too weak, or too strong, indicative of a sensor coil failure. The MCU could be programmed to report errors for unexpected position readings based on the current speed.

# Battery Voltage Monitoring

The MCU is equipped with an internal ADC. One of the ADC input channels is internally connected to a divided down (by 3) version of the VBAT voltage. This allows the MCU to digitize and monitor the battery voltage if a battery is connected. The user can program the MCU to report the battery voltage, and report errors if a battery voltage falls below acceptable levels.

# Temperature Monitoring

The internal MCU can report its own die temperature. The MCU can be programmed to report the internal temperature if desired.

# **MCU Programming**

The NCS32100 comes with default firmware providing the functionality and performance outlined in the NCS32100 Reference Design Users Guide. An NCS32100 SDK Starter Guide is also available which describes how to setup a project in an Eclipse based IDE for programming and debugging firmware. MCU registers and hardware available to the user are all documented in the NCS32100 reference design manual. The SDWIO and SKCLK, and DEBUG\_EN pins are used exclusively for the programming of the embedded NCS32100 MCU using an SWD J–Link programmer.

#### Sensor Speed

The NCS32100 internally calculates the rotor velocity every  $2 \mu s$ . The device can be configured with a velocity low pass filter to help reject noise and velocity jitter. Available filter coefficients are detailed in the configuration register section of this datasheet. The maximum sensor speed at which full accuracy is maintained is specified as 6000 rpm. Higher speeds are possible at reduced accuracy, up to 45000 rpm. These speed limitations are based on the electrical speed defined by the number of periods in the coarse and fine coils. The table below shows the mechanical speeds achievable for different fine coil period settings. The coil period configuration takes place in register 0x5F.

| Fine Coil Period Setting | Maximum Achievable<br>Mechanical Speed (RPM) |

|--------------------------|----------------------------------------------|

| 8                        | 360,000                                      |

| 16                       | 180,000                                      |

| 32                       | 90,000                                       |

| 64                       | 45,000                                       |

| 128                      | 22,500                                       |

| 256                      | 10,000                                       |

If higher mechanical speed capability if needed, then the PCB sensor can be designed with fewer fine coil periods. Position accuracy and PCB size also are affected by the fine coils period selection.

# **Output Modes**

The NCS32100 has four data pins for supporting any interface that can be programmed in firmware. The Data[3:0] pins support any signal between 2.7 V to 5.5 V using internal level shifters where the output voltage levels are powered by the VDDIO. The NCS32100 reference firmware is programmed to support a 2.5 MHz UART over RS485 interface. The Data[3:0] also supports SPI, SSI, and direct GPIO control. The content and organization of the interface frames are defined by firmware. This flexibility allows for modifications to fit the application of the end user. The reference design utilizes the NCS32100's absolute encoding capability, but the firmware could also be designed to create an incremental output to match 3–Phase Mode, Quadrature mode, and other incremental mode standard formats.

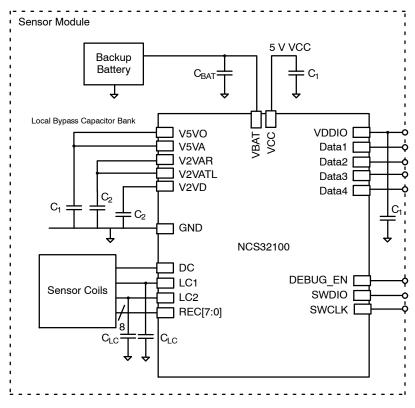

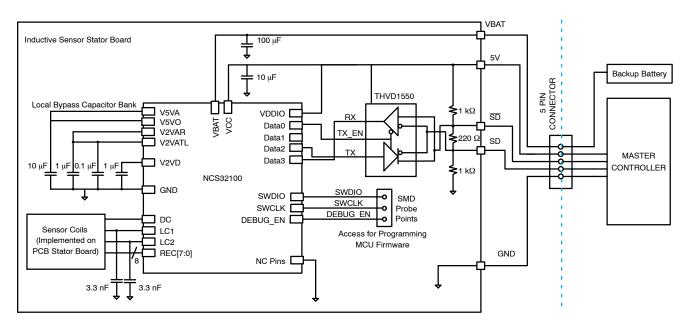

# **TYPICAL APPLICATION**

The following application example presents an angular position sensor application. The internal signal processing is highly configurable. Configuration registers are loaded into the digital logic registers by the internal MCU at power–up. The configuration is thus firmware defined. The design of the coils on the PCB can cater to specific resolution, accuracy, and mechanical envelope constraints. A wide range of applications can thus be targeted by the NCS32100 utilizing different numbers of coil sets to fit different sizes of sensor and accuracies. The diagram below shows the connections needed for a rotary sensor application where the NCS32100 provides the sensor excitation and the sensor receive circuitry.

Figure 4. Typical NCS32100 Application

In this application, an RS-485 driver is used to send the UART data from the NCS32100 out to a twisted differential pair. No other circuitry is needed. The entire encoder module electronics can easily fit on the stator PCB for a lean, low-cost, solution.

# **Typical Sensor Configuration**

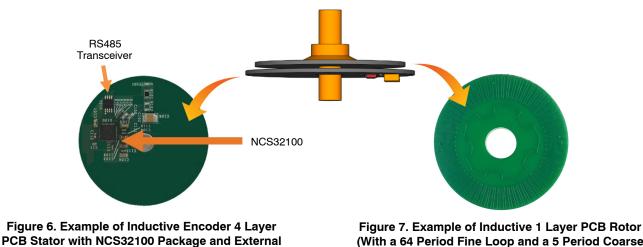

The figures below show the sensor coil configuration used in the NCS32100 reference design. It is one of many possible sensor designs that will work with the NCS32100 device. This sensor design uses two separate coil sets to achieve high accuracy position readings. Sensor coils are connected to the REC pins on the NCS32100, which supports up to 8 coils.

Components on the Back of the Board (Contains

Transmitter Loop and Receiver)

Figure 5. Sensor Electrical Model

# **PCB Considerations**

The layout of the sensor design and it's connection to the NCS32100 must be symmetric to avoid unwanted parasitic coupling. Please refer to the NCS32100 Reference design for an example of correct sensor to NCS32100 interface. The back paddle of the NCS32100 can be used to decrease the thermal resistance and lower the self heating of the part. If a heat spreader plane is connected to the back paddle of the NCS32100, it must not be a solid plane, but rather a series of lines that connect to the back paddle and run out perpendicular to the excitation coil. This is

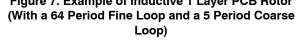

#### Typical Sensor Module (Utilizing the NCS32100)

The NCS32100 can be used with a several configurations and sensors. The example below shows a rotational sensor application, where the NCS32100 is mounted on the stator PCB board and interfaces with the stator coils. Keep out regions and size of the stator / rotor board can change based on application needs regarding design, resolution needs, and accuracy needs.

Figure 8. Mechanical Housing Example

### Effects of Air Gap and Eccentricity and Tilt

The effects of the airgap and misalignment between the rotor and stator in an inductive angular position sensor are highly dependent on the systems mechanical dimensions. The system above is composed of multiple receiver coils on a stator to interface with the NCS32100, and multiple coils on a rotor. The sensors outer diameter is 37.5 mm with a 0.3 mm air-gap between rotor and stator. In this system, the

50 arcsec specification was maintained with  $\pm 0.25$  mm variation on eccentricity, and  $\pm 0.2$  mm variation on the air gap. For sensors with a different diameter and coil configuration, this sensitivity will be different. For assistance with sensor stator and rotor design, application engineering support is available. Please consult your **onsemi** sales contact.

# **APPENDIX A: INTERNAL CONFIGURATION REGISTER DEFINITIONS**

# LC OSCILLATOR GAIN DAC

Address 0x00 - Default Value 0x0000

This register shows the excitation coil oscillator gain. It is a read only register. It is periodically updated by the NCS32100 to get the desired receiver coil magnitudes.

| Bit  | Name                      | Description                                                                                                                                                                                                                                                                                           |

|------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 |                           | Reserved.                                                                                                                                                                                                                                                                                             |

| 7:0  | USER_LC_GAIN_DAC_FSM[7:0] | LC Oscillator Gain drive strengths.<br>The current LC Oscillator Gain DAC value.<br><i>Code Gain Calculation</i><br>0b'00xxxxx 0.4 + (0.05 * N) mA<br>0b'01xxxxx 3.6 + (0.1 * N) mA<br>0b'10xxxxx 10 + (0.2 * N) mA<br>0b'11xxxxx 22.8 + (0.4 * N) mA<br>where 'N' is the 'xxxxx' portion of the code |

# RECEIVER PIN AMPLIFIER GAIN (DAC SETTINGS)

Address 0x01 - Default Value 0x0000

This register shows the programmable amplifier gain setting. It is a read only register. The programmable gain amplifier is used to amplify the receiver coil signals before they are digitized. The programmable gain amplifier settings are periodically updated by the NCS32100 to get the best possible dynamic range on the sensor receiver signals.

| Bit   | Name                              | Description                                                                                                                                                                                                                                                                                            |  |

|-------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15:14 |                                   | Reserved.                                                                                                                                                                                                                                                                                              |  |

| 13:8  | USER_PGA_GAIN_DAC_FSM_COARSE[5:0] | Programmable Amplifier Gain settings for Coarse Coils Block.<br>The current PGA Gain DAC value used by the Coarse block.                                                                                                                                                                               |  |

|       |                                   | NOTE: The PGA Gain $G_{PGA}$ is related to<br>USER_PGA_GAIN_DAC_COARSE[5:0] by the equation:<br>$G_{PGA} = (1.189^USER_PGA_GAIN_DAC_COARSE[5:0]) * 10.$                                                                                                                                                |  |

| 7:6   |                                   | Reserved.                                                                                                                                                                                                                                                                                              |  |

| 5:0   | USER_PGA_GAIN_DAC_FSM_FINE[5:0]   | Programmable Amplifier Gain settings for Fine Coils Block.<br>The current PGA Gain DAC value used by the Fine block.<br>NOTE: The PGA Gain G <sub>PGA</sub> is related to USER_PGA_GAIN_DAC_FINE[5:0]<br>by the equation:<br>G <sub>PGA</sub> = (1.189 <sup>^</sup> USER_PGA_GAIN_DAC_FINE[5:0]) * 10. |  |

# **POSSIBLE GAIN SETTINGS**

| Gain<br>Setting | Gain Setting Code | Gain |

|-----------------|-------------------|------|

| 1               | 0                 |      |

# **DIGITAL CONTROL**

Address 0x03 - Default 0x0000

The Digital Control Register allows the user to turn the angle extrapolation feature on or off. It also allows the user to run the open coil detect check.

| Bit  | Name                   | Description                                                                                                               |  |

|------|------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| 15   | USER_ABSALGO_EXTRP_DIS | User Absolute Algorithm Extrapolation Disable.                                                                            |  |

|      |                        | Disable the angle extrapolation in the absolute algorithm when the LC oscillator gain, PGA gain or PGA offset are updated |  |

| 14   |                        | Reserved.                                                                                                                 |  |

| 13   | USER_OPENCOILDET_RUN   | ER_OPENCOILDET_RUN USER Open Coils Detection Run.                                                                         |  |

|      |                        | Run the open coils detection FSM. The bit is reset to 0 when the FSM is finished.                                         |  |

| 12   |                        | Reserved.                                                                                                                 |  |

| 11   | USER_TURN_RST          | Turn Counter Reset.                                                                                                       |  |

|      |                        | Reset the Turn counter to 0. The register bit is automatically reset to 0                                                 |  |

| 10:0 |                        | Reserved.                                                                                                                 |  |

# STATUS

Address 0x04 – Default 0x0000

The status register holds the results of the open coil detect test.

| Bit   | Name                  | Description                                                                        |

|-------|-----------------------|------------------------------------------------------------------------------------|

| 15:14 |                       | Reserved.                                                                          |

| 13    | USER_OPENCOILDET_FLAG | User Open Coil Detection Flag.<br>A 1 signifies that there is an unconnected coil. |

| 12:0  |                       | Reserved.                                                                          |

# SELECTION MATRIX FOR COARSE BLOCK

Address 0x10 - Default 0xF249

This register holds the setting for the connection between the REC pins and the sensor coarse loops. For more details, see advanced configuration note.

| Bit   | Name                          | Description                                                                                                                                                                                                                                                |  |

|-------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15:14 | SEL_MATRIX_RECT3P_COARSE[1:0] | Selection Matrix for Rectifier3 Positive Input on Coarse block.<br>See table below for decode.                                                                                                                                                             |  |

| 13:12 | SEL_MATRIX_RECT3N_COARSE[1:0] | Selection Matrix for Rectifier3 Negative Input on Coarse block.<br>If SEL_MATRIX_RECT3N_COARSE[1:0] =<br>SEL_MATRIX_RECT3P_COARSE[1:0] then the rectifier3 negative input of the<br>Coarse block is connected to DC. Otherwise see table below for decode. |  |

| 11:10 | SEL_MATRIX_RECT2P_COARSE[1:0] | Selection Matrix for Rectifier2 Positive Input on Coarse Block.<br>See table below for decode.                                                                                                                                                             |  |

| 9:8   | SEL_MATRIX_RECT2N_COARSE[1:0] | Selection Matrix for Rectifier2 Negative Input on Coarse Block.<br>If SEL_MATRIX_RECT2N_COARSE[1:0] =<br>SEL_MATRIX_RECT2P_COARSE[1:0] then the rectifier2 negative input of the<br>Coarse block is connected to DC. Otherwise see table below for decode. |  |

| 7:6   | SEL_MATRIX_RECT1P_COARSE[1:0] | E[1:0] Selection Matrix for Rectifier1 Positive Input on Coarse Block.<br>See table below for decode.                                                                                                                                                      |  |

| 5:4   | SEL_MATRIX_RECT1N_COARSE[1:0] | Selection Matrix for Rectifier1 Negative Input on Coarse Block.<br>If SEL_MATRIX_RECT1N_COARSE[1:0] =<br>SEL_MATRIX_RECT1P_COARSE[1:0] then the rectifier1 negative input of the<br>Coarse block is connected to DC. Otherwise see table below for decode. |  |

| 3:2   | SEL_MATRIX_RECT0P_COARSE[1:0] | Selection Matrix for Rectifier0 Positive Input on Coarse Block.<br>See table below for decode.                                                                                                                                                             |  |

| 1:0   | SEL_MATRIX_RECT0N_COARSE[1:0] | Selection Matrix for Rectifier0 Negative Input on Coarse Block.<br>If SEL_MATRIX_RECTON_COARSE[1:0] =<br>SEL_MATRIX_RECTOP_COARSE[1:0] then the rectifier0 negative input of the<br>Coarse block is connected to DC. Otherwise see table below for decode. |  |

# Table 12. COARSE BLOCK RECTIFIER CONTROL SELECTION

| Coarse Register Input | Channel Select | Pin  |

|-----------------------|----------------|------|

| 00                    | 0              | REC0 |

| 00                    | 1              | REC4 |

| 01                    | 0              | REC1 |

| 01                    | 1              | REC5 |

| 10                    | 0              | REC2 |

| 10                    | 1              | REC6 |

| 11                    | 0              | REC3 |

| 11                    | 1              | REC7 |

# SELECTION MATRIX FOR FINE BLOCK

Address 0x11 - Default 0x0B6D

This register holds the setting for the connection between the REC pins and the sensor fine loops. For more details, see advanced configuration note.

| Bit   | Name                        | Description                                                                                                                                                                                                                                        |

|-------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:14 | SEL_MATRIX_RECT3P_FINE[1:0] | Selection Matrix for Rectifier3 Positive Input on Fine Block.<br>See table below for decode.                                                                                                                                                       |

| 13:12 | SEL_MATRIX_RECT3N_FINE[1:0] | Selection Matrix for Rectifier3 Negative Input on Fine Block.<br>If SEL_MATRIX_RECT3N_FINE[1:0] = SEL_MATRIX_RECT3P_FINE[1:0]<br>then the rectifier3 negative input of the fine block is connected to DC.<br>Otherwise see table below for decode. |

| 11:10 | SEL_MATRIX_RECT2P_FINE[1:0] | Selection Matrix for Rectifier2 Positive Input on Fine Block.<br>See table below for decode.                                                                                                                                                       |

| 9:8   | SEL_MATRIX_RECT2N_FINE[1:0] | Selection Matrix for Rectifier2 Negative Input on Fine Block.<br>If SEL_MATRIX_RECT2N_FINE[1:0] = SEL_MATRIX_RECT2P_FINE[1:0]<br>then the rectifier2 negative input of the fine block is connected to DC.<br>Otherwise see table below for decode. |

| 7:6   | SEL_MATRIX_RECT1P_FINE[1:0] | Selection Matrix for Rectifier1 Positive Input on Fine Block.<br>See table below for decode.                                                                                                                                                       |

| 5:4   | SEL_MATRIX_RECT1N_FINE[1:0] | Selection Matrix for Rectifier1 Negative Input on Fine Block.<br>If SEL_MATRIX_RECT1N_FINE[1:0] = SEL_MATRIX_RECT1P_FINE[1:0]<br>then the rectifier1 negative input of the fine block is connected to DC.<br>Otherwise see table below for decode. |

| 3:2   | SEL_MATRIX_RECT0P_FINE[1:0] | Selection Matrix for Rectifier0 Positive Input on Fine Block.<br>See table below for decode.                                                                                                                                                       |

| 1:0   | SEL_MATRIX_RECTON_FINE[1:0] | Selection Matrix for Rectifier0 Negative Input on Fine Block.<br>If SEL_MATRIX_RECTON_FINE[1:0] = SEL_MATRIX_RECTOP_FINE[1:0]<br>then the rectifier0 negative input of the fine block is connected to DC.<br>Otherwise see table below for decode. |

# Table 13. FINE BLOCK RECTIFIER CONTROL SELECTION

| Coarse Register Input | Channel Select | Pin  |

|-----------------------|----------------|------|

| 00                    | 0              | REC4 |

| 00                    | 1              | REC0 |

| 01                    | 0              | REC5 |

| 01                    | 1              | REC1 |

| 10                    | 0              | REC6 |

| 10                    | 1              | REC2 |

| 11                    | 0              | REC7 |

| 11                    | 1              | REC3 |

The next 16 registers hold the calibration coefficients used to calibrate out any sensor non–linearity. See the calibration section for more details.

# CLARKE TRANSFORM IMAGINARY COEFFICIENT 0 FOR COARSE BLOCK

Address 0x12 - Default 0x0000

| Bit  | Name                     | Description                                                                                                                                                                                                                                                                                  |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | CLARKE_COARSE_IM_A[15:0] | Filter 0 Clarke Transform Imaginary Coefficient for Coarse Block.<br>An Imaginary Coefficient of the Clarke Transform. This coefficient is applied to<br>the Filter/Rectifier 0 output of the Coarse Block. This register is a fixed point<br>number with 14 sign bits, in Q format as Q2.14 |

# CLARKE TRANSFORM IMAGINARY COEFFICIENT 1 FOR COARSE BLOCK

Address 0x13 - Default 0x0000

| Bit  | Name                     | Description                                                                                                                                                                                                                                                                                  |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | CLARKE_COARSE_IM_B[15:0] | Filter 1 Clarke Transform Imaginary Coefficient for Coarse Block.<br>An Imaginary Coefficient of the Clarke Transform. This coefficient is applied to<br>the Filter/Rectifier 1 output of the Coarse Block. This register is a fixed point<br>number with 14 sign bits, in Q format as Q2.14 |

# CLARKE TRANSFORM IMAGINARY COEFFICIENT 2 FOR COARSE BLOCK

Address 0x14 - Default 0x0000

| Bit  | Name                     | Description                                                                                                                                                                                                                                                                                  |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | CLARKE_COARSE_IM_C[15:0] | Filter 2 Clarke Transform Imaginary Coefficient for Coarse Block.<br>An Imaginary Coefficient of the Clarke Transform. This coefficient is applied to<br>the Filter/Rectifier 2 output of the Coarse Block. This register is a fixed point<br>number with 14 sign bits, in Q format as Q2.14 |

# CLARKE TRANSFORM IMAGINARY COEFFICIENT 3 FOR COARSE BLOCK

Address 0x15 - Default 0x0000

| Bit  | Name                     | Description                                                                                                                                                                                                                                                                                  |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | CLARKE_COARSE_IM_D[15:0] | Filter 3 Clarke Transform Imaginary Coefficient for Coarse Block.<br>An Imaginary Coefficient of the Clarke Transform. This coefficient is applied to<br>the Filter/Rectifier 3 output of the Coarse Block. This register is a fixed point<br>number with 14 sign bits, in Q format as Q2.14 |

# CLARKE TRANSFORM REAL COEFFICIENT 0 FOR COARSE BLOCK

Address 0x16 - Default 0x0000

| Bit  | Name                     | Description                                                                                                                                                                                                                                                                       |

|------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | CLARKE_COARSE_RE_A[15:0] | Filter 0 Clarke Transform Real Coefficient for Coarse Block.<br>A Real Coefficient of the Clarke Transform. This coefficient is applied to the<br>Filter/Rectifier 0 output of the Coarse Block. This register is a fixed point<br>number with 14 sign bits, in Q format as Q2.14 |

# CLARKE TRANSFORM REAL COEFFICIENT 1 FOR COARSE BLOCK

Address 0x17 - Default 0x0000

| Bit  | Name                     | Description                                                                                                                                                                                                                                                                       |

|------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | CLARKE_COARSE_RE_B[15:0] | Filter 1 Clarke Transform Real Coefficient for Coarse Block.<br>A Real Coefficient of the Clarke Transform. This coefficient is applied to the<br>Filter/Rectifier 1 output of the Coarse Block. This register is a fixed point<br>number with 14 sign bits, in Q format as Q2.14 |

# CLARKE TRANSFORM REAL COEFFICIENT 2 FOR COARSE BLOCK

Address 0x18 - Default 0x0000

| Bit  | Name                     | Description                                                                                                                                                                                                                                                                       |

|------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | CLARKE_COARSE_RE_C[15:0] | Filter 2 Clarke Transform Real Coefficient for Coarse Block.<br>A Real Coefficient of the Clarke Transform. This coefficient is applied to the<br>Filter/Rectifier 2 output of the Coarse Block. This register is a fixed point<br>number with 14 sign bits, in Q format as Q2.14 |

# CLARKE TRANSFORM REAL COEFFICIENT 3 FOR COARSE BLOCK

Address 0x19 - Default 0x0000