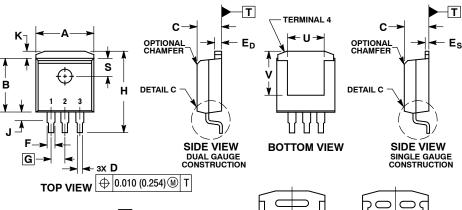

# D2PAK CASE 418AF ISSUE E

**DATE 15 SEP 2015**

**BOTTOM VIEW OPTIONAL CONSTRUCTIONS**

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: INCHES.

TAB CONTOUR OPTIONAL WITHIN DIMENSIONS

- DIMENSIONS U AND V ESTABLISH A MINIMUM MOUNTING SURFACE FOR TERMINAL 4.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH OR GATE PROTRUSIONS. MOLD FLASH AND GATE PROTRUSIONS NOT TO EXCEED 0.025 (0.635) MAXIMUM.

- SINGLE GAUGE DESIGN WILL BE SHIPPED AF-TER FPCN EXPIRATION IN OCTOBER 2011.

|     | INCHES    |       | MILLIMETERS |        |

|-----|-----------|-------|-------------|--------|

| DIM | MIN       | MAX   | MIN         | MAX    |

| Α   | 0.386     | 0.403 | 9.804       | 10.236 |

| В   | 0.356     | 0.368 | 9.042       | 9.347  |

| С   | 0.170     | 0.180 | 4.318       | 4.572  |

| D   | 0.026     | 0.036 | 0.660       | 0.914  |

| ED  | 0.045     | 0.055 | 1.143       | 1.397  |

| Es  | 0.018     | 0.026 | 0.457       | 0.660  |

| F   | 0.051 REF |       | 1.295 REF   |        |

| G   | 0.100 BSC |       | 2.540 BSC   |        |

| Н   | 0.539     | 0.579 | 13.691      | 14.707 |

| J   | 0.125 MAX |       | 3.175 MAX   |        |

| K   | 0.050 REF |       | 1.270 REF   |        |

| L   | 0.000     | 0.010 | 0.000       | 0.254  |

| M   | 0.088     | 0.102 | 2.235       | 2.591  |

| N   | 0.018     | 0.026 | 0.457       | 0.660  |

| P   | 0.058     | 0.078 | 1.473       | 1.981  |

| R   | 0°        | 8°    | 0°          | 8°     |

| S   | 0.116 REF |       | 2.946 REF   |        |

| U   | 0.200 MIN |       | 5.080 MIN   |        |

| ٧   | 0.250 MIN |       | 6.350 MIN   |        |

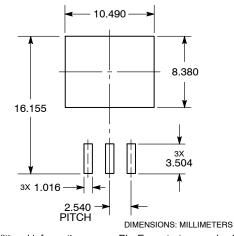

## **SOLDERING FOOTPRINT\***

**DETAIL C**

T

SEATING PLANE

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

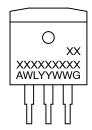

### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code

= Assembly Location

= Wafer Lot WL YY = Year WW = Work Week G = Pb-Free Package

| DOCUMENT NUMBER: | 98AON21981D | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | D2PAK       |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

<sup>\*</sup>This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G", may or not be present.